## NVMe<sup>™</sup> Management Interface (NVMe-MI<sup>™</sup>) Workgroup Update

Sponsored by NVM Express® organization, the owner of NVMe™, NVMe-oF™ and NVMe-MI™ standards

Austin Bolen

DELLEMC

Myron Loewen

### Agenda

- NVMe-MI<sup>™</sup> Workgroup Update

- NVMe-MI 1.0a Overview

- What's new in NVMe-MI 1.1

- In-band NVMe-MI

- Enclosure Management

- Managing Multi NVM Subsystem Devices

- Summary

### NVM Express<sup>®</sup>, Inc. 120+ Companies defining NVMe<sup>™</sup> together

### Board of Directors

13 elected companies, stewards of the technology & driving processes Chair: Amber Huffman

### Marketing Workgroup

NVMexpress.org, webcasts, tradeshows, social media, and press Co-Chairs: Janene Ellefson and Jonmichael Hands

### **Technical** Workgroup

NVMe Base and NVMe Over Fabrics Chair<sup>.</sup> Amber Huffman

### Management Intf. Workgroup

Out-of-band management over SMBus and PCIe® VDM Chair: Peter Onufryk Vice Chair: Austin Bolen

ախորհ

### Interop (ICC) Workgroup

Interop & Conformance Testing in collaboration with UNH-IOL Chair: Ryan Holmqvist

ORACLE

DELLEMC

SEAGATE

5

EXPRESS

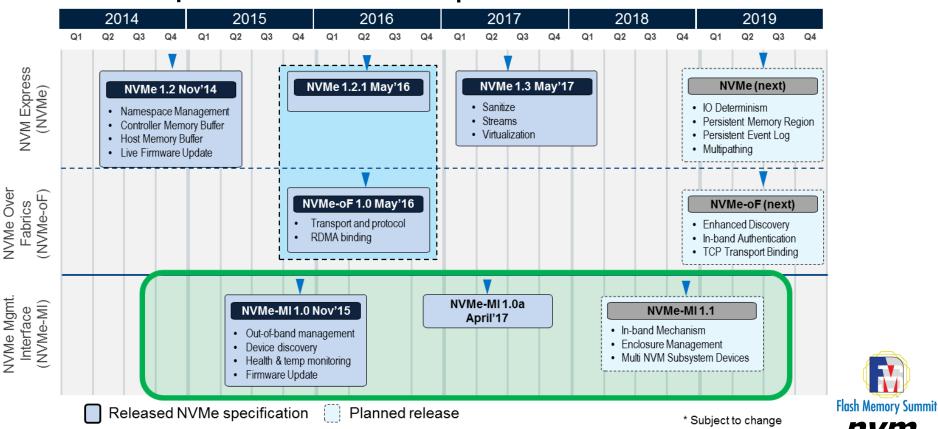

### NVM Express<sup>™</sup> Roadmap

### NVMe-MI<sup>™</sup> Ecosystem

- Commercial test equipment for NVMe-MI

- NVMe-MI 1.0a compliance testing program has been developed

- Compliance testing started in the May 2017 NVMe<sup>™</sup> Plugfest conducted by the University of New Hampshire Interoperability Laboratory (UNH-IOL)

- 7 devices from multiple vendors have passed compliance testing and are on the NVMe-MI Integrators List

- Servers are shipping that support NVMe-MI

### What is the NVMe<sup>™</sup> Management Interface 1.0a?

A programming interface that allows out-of-band management of an NVMe Storage Device Field Replaceable Unit (FRU)

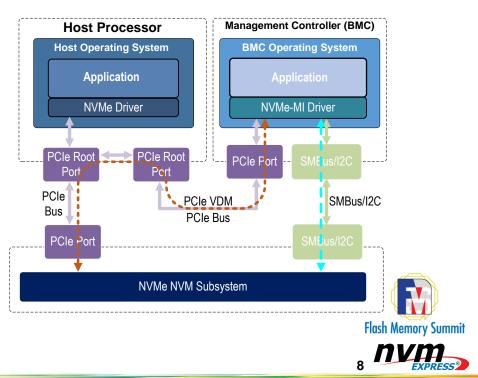

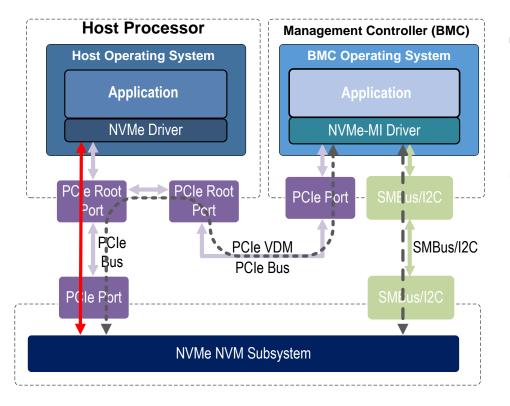

# Out-of-Band Management and NVMe-MI™

Out-of-Band Management – Management that operates with hardware resources and components that are *independent of the host operating system control*

- NVMe<sup>™</sup> Out-of-Band Management Interfaces

- SMBus/I2C

- PCIe Vendor Defined Messages (VDM)

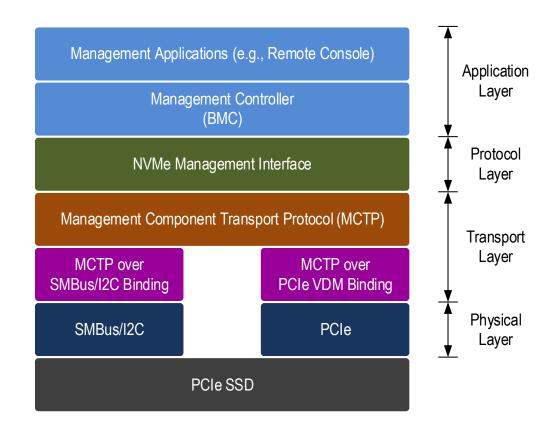

### NVMe-MI<sup>™</sup> Out-of-Band Protocol Layering

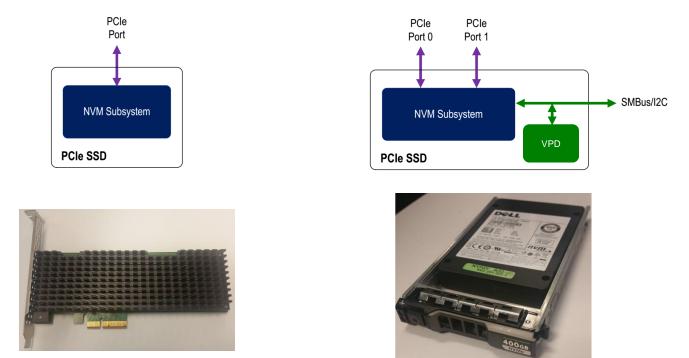

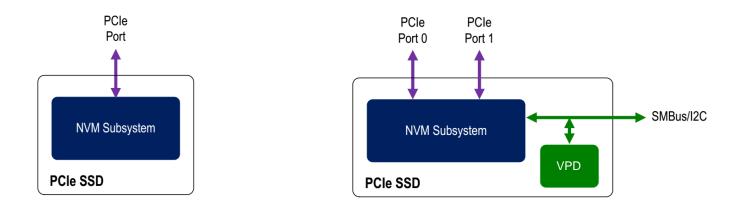

### NVMe<sup>™</sup> Storage Device in 1.0a

NVMe Storage Device – One NVM Subsystem with one or more ports, vital product data (VPD), and an optional SMBus/I2C interface

### In-Band Management and NVMe-MI<sup>™</sup>

- In-band mechanism allows application to tunnel NVMe-MI commands through NVMe<sup>™</sup> driver

- Two new NVMe Admin commands

- NVMe-MI Send

- NVMe-MI Receive

#### Benefits

- Provides management capabilities not available in-band via NVMe commands

- Efficient NVM Subsystem health status reporting

- Ability to manage NVMe at a FRU level

- Vital Product Data (VPD) access

- Enclosure management

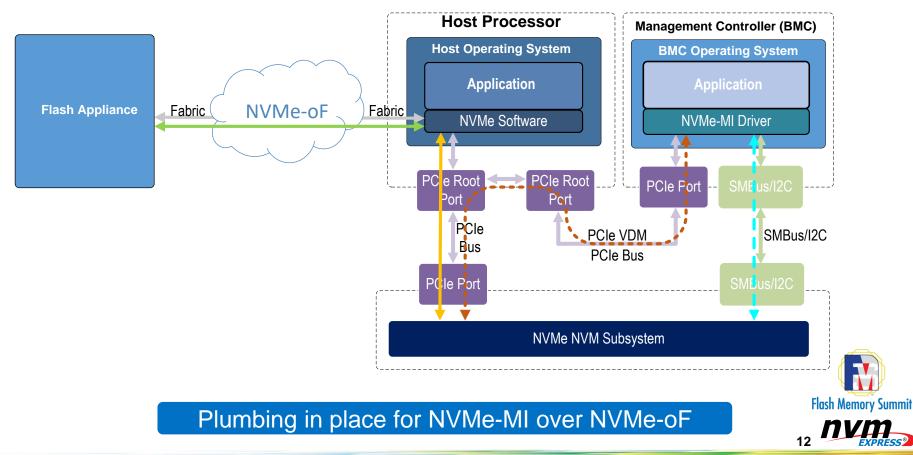

### NVMe-MI<sup>™</sup> over NVMe-oF<sup>™</sup>

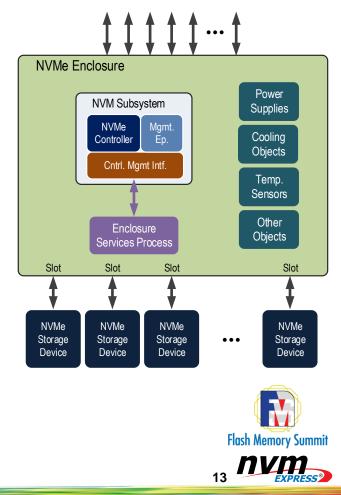

### **Enclosure Management**

- SES Based Enclosure Management

- Technical proposal developed in NVMe-MI™ workgroup

- While the NVMe<sup>™</sup> and SCSI architectures differ, the elements of an enclosure and the capabilities required to manage these elements are the same

- Example enclosure elements: power supplies, fans, display or indicators, locks, temperature sensors, current sensors, voltage sensors, and ports

- Comprehensive enclosure management that leverages SCSI Enclosure Services (SES), a standard developed by T10 for management of enclosures using the SCSI architecture

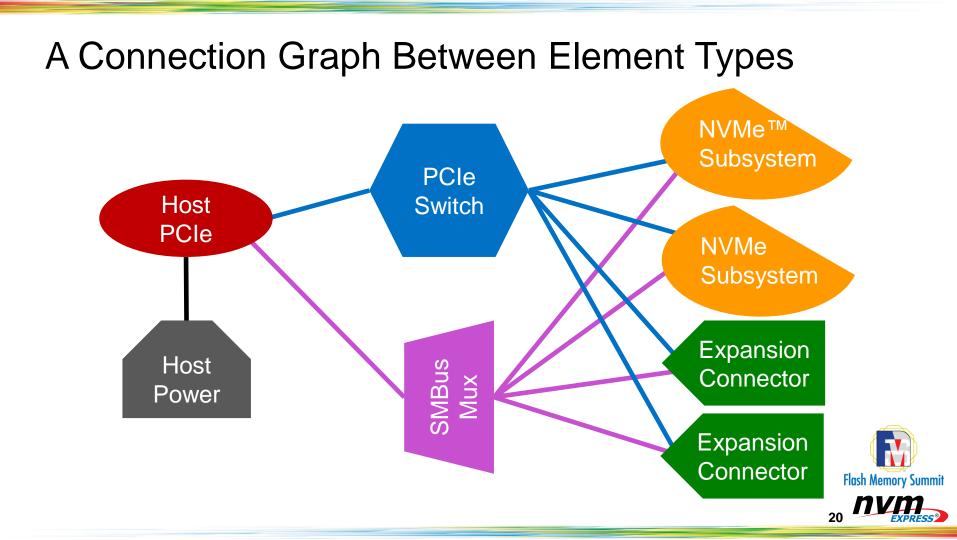

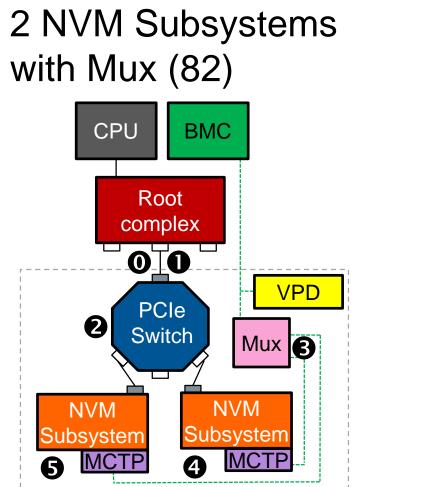

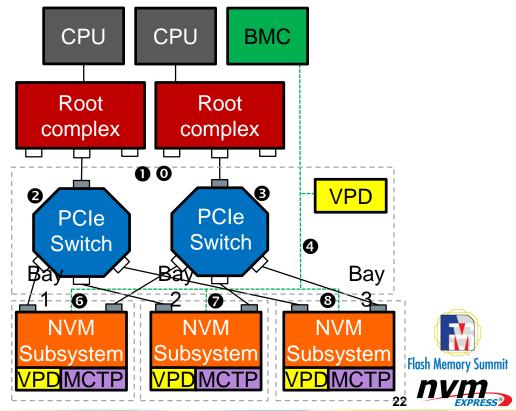

# Multi NVM Subsystem Management

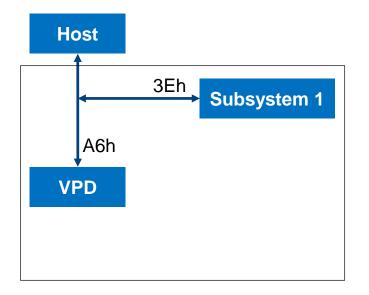

### NVMe-MI<sup>™</sup> 1.0a NVMe<sup>™</sup> Storage Device

NVM Storage Device – One NVM Subsystem with one or more ports and an optional SMBus/I2C interface

Single Ported PCIe SSD

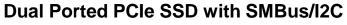

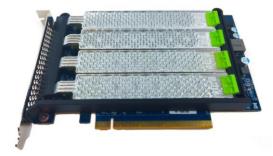

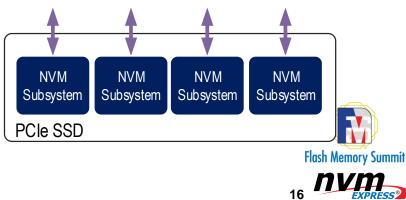

### NVMe<sup>™</sup> Storage Device with Multiple NVM Subsystems

M.2 Carrier Board from Amfeltec

#### ANA Carrier Board from Facebook

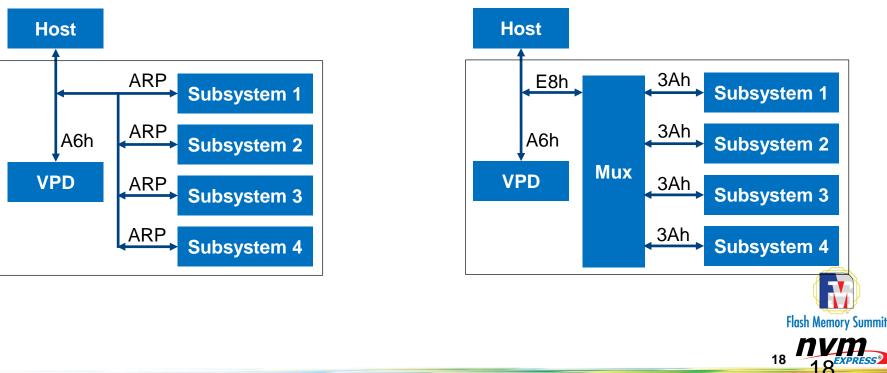

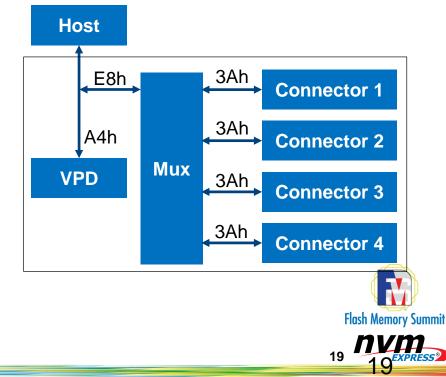

### SMBus Topology for NVMe-MI<sup>™</sup> 1.0

## Multiple NVM Subsystems on a single SMBus Port

- Describe topology in new VPD MultiRecord

- Add UDID types for additional devices like Mux

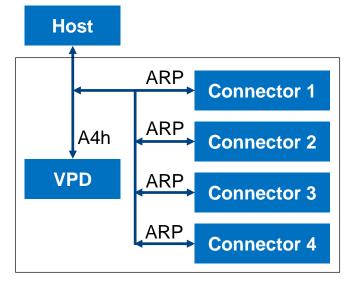

# Support Expansion Connectors

- New VPD address to avoid conflicts with plugged in devices

- Optional Labels for each connector to assist technicians

### Single Port Example (35 bytes of 256B EEPROM)

|                    | CP | U               | BMC           |             | Record:              | Record                   | Record                 | Record               | Header                 | Version                | Rsvd                   | Element                                                                   |  |

|--------------------|----|-----------------|---------------|-------------|----------------------|--------------------------|------------------------|----------------------|------------------------|------------------------|------------------------|---------------------------------------------------------------------------|--|

|                    |    |                 |               | Header      |                      |                          |                        |                      | Chcksm<br>75h          |                        | 00h                    | Count<br>03h                                                              |  |

|                    | (  | Root<br>complex |               |             | Type:<br>Host<br>01h | Element<br>Length<br>08h | Form<br>Factor<br>12h  | SMBus<br>Dest<br>02h | Link<br>Options<br>00h | Link 0<br>Width<br>84h | Link 0<br>Start<br>00h | Link 0<br>Dest.<br>02h                                                    |  |

|                    |    |                 |               | Element     |                      | Element<br>Length<br>08h | Thermal<br>Load<br>0Fh | Vaux<br>Load<br>32h  | Rail<br>Options<br>00h | Rail<br>Voltage<br>78h | 12V<br>initial<br>08h  | 12V<br>max<br>0Fh                                                         |  |

| NVM 2<br>Subsystem |    |                 |               | Elemen<br>2 | Type:<br>NVMe<br>09h | Element<br>Length<br>13h | MCTP<br>Address<br>3Ah |                      | PCIe<br>Ports<br>12h   | Port 0<br>Speed<br>0Fh | Port 0<br>Flags<br>01h | Total NVM Capacity<br>(MSB first)<br>000000000000000000000000000000000000 |  |

|                    | N  | <u>ICTP</u>     | ······[<br>VP | D           | _                    |                          |                        |                      |                        |                        |                        |                                                                           |  |

# Dual Port with Expansion Connectors (78)

# Summary

- NVMe-MI<sup>™</sup> 1.0a is gaining market acceptance and is available in shipping products

- NVMe-MI 1.1 is nearing completion

- Significant new features

- In-band mechanism

- Enclosure management

- Support for multi NVM subsystem management

- It is time to start thinking about anchor features for NVMe-MI 1.2

## Additional Material on NVMe-MI™

- BrightTALK Webinar

- o https://www.brighttalk.com/webcast/12367/282765/the-nvme-management-interface-nvme-mi-learn-whats-new

- Flash Memory Summit 2017

- o Slides: <u>https://www.flashmemorysummit.com/English/Collaterals/Proceedings/2017/20170808\_FA12\_PartA.pdf</u>

- o Video:

- o <u>https://www.youtube.com/watch?v=daKL7tlvNII</u>

- o <a href="https://www.youtube.com/watch?v=Daqj-XqlCo8">https://www.youtube.com/watch?v=Daqj-XqlCo8</a>

- Flash Memory Summit 2015

- o Slides: <u>https://www.flashmemorysummit.com/English/Collaterals/Proceedings/2015/20150811\_FA11\_Carroll.pdf</u>

- Flash Memory Summit 2014

- o Slides: https://www.flashmemorysummit.com/English/Collaterals/Proceedings/2014/20140804\_SeminarF\_Onufryk\_Bolen.pdf

- NVMe-MI Specification

- o https://nvmexpress.org/resources/specifications/

MCTP Overview: <a href="http://dmtf.org/sites/default/files/standards/documents/DSP2016.pdf">http://dmtf.org/sites/default/files/standards/documents/DSP2016.pdf</a>

MCTP Base Spec: https://www.dmtf.org/sites/default/files/standards/documents/DSP0236\_1.3.0.pdf

MCTP SMBus/I2C Binding: https://www.dmtf.org/sites/default/files/standards/documents/DSP0237\_1.1.0.pdf

MCTP PCIe VDM Binding: https://www.dmtf.org/sites/default/files/standards/documents/DSP0238\_1.0.2.pdf

IPMI Platform Management FRU Information Storage Definition: https://www.intel.la/content/www/xl/es/servers/ipmi/ipmi-platform-mgt-fru-infostorage-def-v1-0-rev-1-3spec-update.html