# **NVM Express<sup>™</sup>**

# **Management Interface**

**Revision 1.1b**

October 5, 2020

Please send comments and questions to info@nvmexpress.org

The NVM Express<sup>™</sup> Management Interface revision 1.1b specification is available for download at http://nvmexpress.org. The NVM Express Management Interface revision 1.1b specification incorporates the NVM Express Management Interface revision 1.0a specification ratified on April 8<sup>th</sup> 2017 along with NVMe-MI 1.0a ECN 001, ECN 002, and ECN 003, TP 6001, TP 6002, TP 6003, TP 6004, TP 6005, TP 6006, TP 6007, and editorial changes including applying the NVM Express<sup>™</sup> trademark guidelines. It also consists of the NVM Express Management Interface revision 1.1 specification ratified on April 29<sup>th</sup>, 2019 along with NVMe-MI 1.1 ECN 001 and ECN 002.

SPECIFICATION DISLAIMER

#### LEGAL NOTICE:

© Copyright 2007 to 2020 NVM Express, Inc. ALL RIGHTS RESERVED.

This NVM Express Management Interface revision 1.1b specification is proprietary to the NVM Express, Inc. (also referred to as "Company") and/or its successors and assigns.

**NOTICE TO USERS WHO ARE NVM EXPRESS, INC. MEMBERS**: Members of NVM Express, Inc. have the right to use and implement this NVM Express Management Interface revision 1.1b specification subject, however, to the Member's continued compliance with the Company's Intellectual Property Policy and Bylaws and the Member's Participation Agreement.

**NOTICE TO NON-MEMBERS OF NVM EXPRESS, INC.**: If you are not a Member of NVM Express, Inc. and you have obtained a copy of this document, you only have a right to review this document or make reference to or cite this document. Any such references or citations to this document must acknowledge NVM Express, Inc. copyright ownership of this document. The proper copyright citation or reference is as follows: "© 2007 to 2020 NVM Express, Inc. ALL RIGHTS RESERVED." When making any such citations or references to this document you are not permitted to revise, alter, modify, make any derivatives of, or otherwise amend the referenced portion of this document in any way without the prior express written permission of NVM Express, Inc. Nothing contained in this document shall be deemed as granting you any kind of license to implement or use this document or the specification described therein, or any of its contents, either expressly or impliedly, or to any intellectual property owned or controlled by NVM Express, Inc., including, without limitation, any trademarks of NVM Express, Inc.

#### LEGAL DISCLAIMER:

THIS DOCUMENT AND THE INFORMATION CONTAINED HEREIN IS PROVIDED ON AN "**AS IS**" BASIS. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, NVM EXPRESS, INC. (ALONG WITH THE CONTRIBUTORS TO THIS DOCUMENT) HEREBY DISCLAIM ALL REPRESENTATIONS, WARRANTIES AND/OR COVENANTS, EITHER EXPRESS OR IMPLIED, STATUTORY OR AT COMMON LAW, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, VALIDITY, AND/OR NONINFRINGEMENT.

All product names, trademarks, registered trademarks, and/or servicemarks may be claimed as the property of their respective owners.

The NVM Express<sup>®</sup> design mark is a registered trademark of NVM Express, Inc.

NVM Express Workgroup c/o VTM, Inc. 3855 SW 153rd Drive Beaverton, OR 97003 USA info@nvmexpress.org

# **Table of Contents**

| 1 | INTRO            | DUCTION                                                                | 6  |

|---|------------------|------------------------------------------------------------------------|----|

|   | 1.1 O            | )verview                                                               | 6  |

|   | 1.2 S            | соре                                                                   | 6  |

|   | 1.2.1            | Outside of Scope                                                       |    |

|   | 1.3 T            | heory of Operation                                                     |    |

|   | 1.3.1            | Out-of-Band Theory of Operation                                        | 7  |

|   | 1.3.2            | In-Band Theory of Operation                                            |    |

|   | 1.4 N            | VM Subsystem Architectural Model                                       | 8  |

|   |                  | VMe Storage Device Architectural Model                                 |    |

|   |                  | VMe Enclosure Architectural Model                                      |    |

|   |                  | conventions                                                            |    |

|   |                  | lefinitions                                                            |    |

|   | 1.8.1            | Carrier                                                                |    |

|   | 1.8.2            | Command Message                                                        |    |

|   | 1.8.3            | Command Slot                                                           |    |

|   | 1.8.4            | Control Primitive                                                      |    |

|   | 1.8.5            | NVMe Controller (Controller)                                           |    |

|   | 1.8.6            | NVMe Controller Management Interface (Controller Management Interface) |    |

|   | 1.8.7            | Enclosure Management                                                   |    |

|   | 1.8.8            | Enclosure Services Process                                             |    |

|   | 1.8.9            | Expansion Connector                                                    |    |

|   | 1.8.10           | Field-Replaceable Unit (FRU)                                           |    |

|   | 1.8.11           | FRU Information Device                                                 |    |

|   | 1.8.12           | In-Band                                                                |    |

|   | 1.8.13           | Management Controller                                                  |    |

|   | 1.8.14           |                                                                        |    |

|   | 1.8.15           | Management Endpoint Buffer                                             |    |

|   | 1.8.16           | NVMe Enclosure                                                         |    |

|   | 1.8.17<br>1.8.18 | NVMe Processing<br>NVMe Storage Device                                 |    |

|   | 1.8.19           | NVMe Storage Device FRU                                                |    |

|   | 1.8.20           | NVMe Storage Device (Rosenclosure)                                     |    |

|   | 1.8.21           | NVMe-MI Message                                                        |    |

|   | 1.8.22           | NVM Subsystem                                                          |    |

|   | 1.8.23           | Out-of-Band                                                            |    |

|   | 1.8.24           |                                                                        |    |

|   | 1.8.25           | Request Message                                                        |    |

|   | 1.8.26           | Requester                                                              |    |

|   | 1.8.27           | Responder                                                              |    |

|   | 1.8.28           | Response Message                                                       |    |

|   | 1.8.29           | SMBus/I2C Mux                                                          |    |

|   | 1.8.30           |                                                                        |    |

|   | 1.8.31           | VPD or Vital Product Data                                              |    |

|   |                  | eywords                                                                |    |

|   | 1.9.1            | mandatory                                                              |    |

|   | 1.9.2            | may                                                                    |    |

|   | 1.9.3            | optional                                                               |    |

|   | 1.9.4            | R                                                                      |    |

|   | 1.9.5<br>1.9.6   | reserved                                                               |    |

|   | 1.9.6            | shall                                                                  |    |

|   |                  | should<br>yte, Word, and Dword Relationships                           |    |

|   |                  | eferences                                                              |    |

|   | 1.11 K           |                                                                        |    |

| 2 | PHYS             | ICAL LAYER                                                             | 27 |

| 2.1         | PCI Express                                                          |     |

|-------------|----------------------------------------------------------------------|-----|

| 2.2         | SMBus/I2C                                                            |     |

| 2.3         | Error Handling                                                       |     |

| 3 Me        | ESSAGE TRANSPORT                                                     | 31  |

| 3.1         | NVMe-MI Messages                                                     |     |

| 3.1         |                                                                      |     |

| 3.2         | Out-of-Band Message Transport                                        |     |

| 3.2         |                                                                      |     |

| 3.2<br>3.3  | .2 Out-of-Band Error Handling<br>In-Band Tunneling Message Transport |     |

| 3.3         | In-Band Tunneling Message Transport                                  |     |

| 4 Me        | essage Servicing Model                                               | 39  |

| 4.1         | NVMe-MI Messages                                                     |     |

| 4.1         | .1 Request Messages                                                  |     |

| 4.1         |                                                                      |     |

| 4.2         | Out-of-Band Message Servicing Model                                  |     |

| 4.2<br>4.2  |                                                                      |     |

| 4.2         |                                                                      |     |

| 4.3         | In-Band Tunneling Message Servicing Model                            |     |

| 4.3         | .1 NVMe-MI Send Command                                              | 55  |

| 4.3         | .2 NVMe-MI Receive Command                                           | 62  |

| 5 MA        | ANAGEMENT INTERFACE COMMAND SET                                      | 68  |

| 5.1         | Configuration Get                                                    | 71  |

| 5.1         |                                                                      |     |

| 5.1         |                                                                      |     |

| 5.1         | .3 MCTP Transmission Unit Size (Configuration Identifier 03h)        | 73  |

| 5.2         | Configuration Set                                                    |     |

| 5.2         |                                                                      |     |

| 5.2<br>5.2  |                                                                      |     |

| 5.3         |                                                                      |     |

| 5.3         |                                                                      |     |

| 5.3         | .2 Filtering by Controller Health Status Changed Flags               | 80  |

| 5.4         | Management Endpoint Buffer Read                                      |     |

| 5.5         | Management Endpoint Buffer Write                                     |     |

| 5.6         | NVM Subsystem Health Status Poll                                     |     |

| 5.7         | Read NVMe-MI Data Structure                                          |     |

| 5.8         | Reset                                                                |     |

| 5.9<br>5.10 | SES Receive<br>SES Send                                              |     |

| 5.10        | VPD Read                                                             |     |

|             | VPD Write                                                            |     |

|             | /M Express Admin Command Set                                         |     |

| 6 NV        |                                                                      |     |

| 6.1         | Request and Response Data                                            |     |

| 6.2         | Status                                                               |     |

| 6.3         | Sanitize Operation                                                   | 105 |

| 7 PC        | IE COMMAND SET (OPTIONAL)                                            | 107 |

| 7.1         | PCIe Configuration Read                                              | 109 |

| 7.2                                                               | PCIe Configuration Write                             |     |  |  |  |  |

|-------------------------------------------------------------------|------------------------------------------------------|-----|--|--|--|--|

| 7.3                                                               | PCIe I/O Read                                        |     |  |  |  |  |

| 7.4                                                               | PCIe I/O Write                                       |     |  |  |  |  |

| 7.5                                                               | PCIe Memory Read                                     |     |  |  |  |  |

| 7.6                                                               | PCIe Memory Write                                    |     |  |  |  |  |

| • • • •                                                           |                                                      |     |  |  |  |  |

| 8 N\                                                              | /M Express Management Enhancements                   | 115 |  |  |  |  |

| 8.1                                                               | Identify Controller                                  |     |  |  |  |  |

| 8.2                                                               | Management Interface Specific Features               |     |  |  |  |  |

| 8.2                                                               |                                                      |     |  |  |  |  |

| 8.2                                                               |                                                      |     |  |  |  |  |

| 9 MA                                                              | ANAGEMENT ARCHITECTURE                               | 120 |  |  |  |  |

| 9 IVIA                                                            |                                                      |     |  |  |  |  |

| 9.1                                                               | Out-of-Band Operational Times                        |     |  |  |  |  |

| 9.2                                                               | Vital Product Data                                   |     |  |  |  |  |

| 9.2                                                               | .1 Common Header                                     |     |  |  |  |  |

| 9.2                                                               |                                                      |     |  |  |  |  |

| 9.2                                                               |                                                      |     |  |  |  |  |

| 9.2                                                               |                                                      |     |  |  |  |  |

| 9.2                                                               |                                                      |     |  |  |  |  |

| 9.3                                                               |                                                      |     |  |  |  |  |

| 9.3                                                               |                                                      |     |  |  |  |  |

| 9.3                                                               |                                                      |     |  |  |  |  |

| 9.3                                                               | ······································               |     |  |  |  |  |

| 9.3                                                               |                                                      |     |  |  |  |  |

| 9.4                                                               | Security                                             | 142 |  |  |  |  |

| APPENDIX A – TECHNICAL NOTE: NVM EXPRESS BASIC MANAGEMENT COMMAND |                                                      |     |  |  |  |  |

| APPENDIX B – EXAMPLE MCTP MESSAGES & MESSAGE INTEGRITY CHECK      |                                                      |     |  |  |  |  |

|                                                                   |                                                      |     |  |  |  |  |

| APPEN                                                             | Appendix C – Example NVMe-MI Messages over SMBus/I2C |     |  |  |  |  |

# 1 Introduction

# 1.1 Overview

The NVM Express<sup>™</sup> (NVMe<sup>™</sup>) interface is a register-level interface that allows in-band host software to communicate with an NVM Subsystem. Since this specification builds on the NVM Express specification, knowledge of the NVM Express specification is assumed.

This specification defines several mechanisms to manage NVMe Storage Devices (refer to section 1.8.18) or NVMe Enclosures (refer to section 1.8.16). One mechanism allows a Management Controller to communicate out-of-band with an NVMe Storage Device or NVMe Enclosure over one or more external interfaces. Another mechanism is the in-band tunneling mechanism which allows the NVMe-MI Management Interface Command Set to be tunneled in-band via the NVMe Admin Commands NVMe-MI Send and NVMe-MI Receive to an NVMe Storage Device or NVMe Enclosure. Refer to the NVM Express specification and section 4.3 of this specification for additional details on the NVMe-MI Send and NVMe-MI Receive commands.

NVMe Storage Devices and NVMe Enclosures that comply with this specification are allowed to support only the out-of-band mechanism, only the in-band tunneling mechanism, or both the out-of-band mechanism and in-band tunneling mechanism.

# 1.2 Scope

This specification defines an architecture and command set for out-of-band and in-band management of an NVMe Storage Device as well as an architecture and mechanisms for monitoring and controlling the elements of an NVMe Enclosure.

This specification defines the following key capabilities for NVMe Storage Devices:

- Discover NVMe Storage Devices that are present and learn capabilities of each NVMe Storage Device;

- Store data about the host environment enabling a Management Controller or other entity to query the data later;

- Health and temperature monitoring;

- Multiple concurrent commands to prevent a long latency command from blocking monitoring operations;

- Out-of-band mechanism is host processor and operating system agnostic;

- A standard format for VPD and defined mechanisms to read/write VPD contents; and

- Preserves data-at-rest security.

This specification defines the following key capabilities for NVMe Enclosures:

- Discover NVMe Enclosures and learn their capabilities;

- Manage and sense the state of NVMe Enclosure elements such as power supplies, cooling devices, displays, and indicators;

- Multiple concurrent commands to prevent a long latency command from blocking monitoring operations;

- Out-of-band mechanism is host processor and operating system agnostic;

- Discover NVMe Storage Devices that are present in Enclosure slots; and

- Preserves data-at-rest security.

# 1.2.1 Outside of Scope

The architecture and command set are specified apart from any usage model. This specification does not specify whether the NVMe interface is used to implement a solid-state drive, a main memory, a cache memory, a backup memory, a redundant memory, etc. Specific usage models are outside the scope of this specification.

This interface is NVM technology agnostic and is specified at a level that abstracts implementation details associated with any specific NVM technology. For example, NAND wear leveling, block erases, and other management tasks are abstracted.

The implementation or use of other published specifications referred to in this specification, even if required for compliance with the specification, are outside the scope of this specification (e.g., PCI Express, SMBus/I2C and MCTP).

The management of NVMe over Fabrics is outside the scope of this specification. This specification does not define new security mechanisms.

This specification does not cover management of non-transparent bridges or PCIe switches. Co-ordination between multiple Requesters or a Requester and a device other than a Responder is outside the scope of this specification. Refer to section 1.8 for the definitions of Requester and Responder.

Coordinating concurrency resulting from operations associated with multiple Responders or between host and Management Endpoint operations is outside the scope of this specification.

The specification of specific Enclosure elements that make up an NVMe Enclosure is outside the scope of this specification. Support for cards or modules that connect to a device slot element (slot) of an NVMe Enclosure, that are not NVMe Storage Devices (e.g., GPUs or FPGAs) is outside the scope of this specification.

An enclosure may support comprehensive management capabilities using SCSI Enclosure Services, basic management capabilities using transport specific mechanisms, or no management capabilities. An example of basic enclosure management capabilities is Native PCIe Enclosure Management (NPEM) specified by the PCI-SIG for PCI Express. The specification of such transport specific basic management capabilities is outside the scope of this specification. This specification only defines comprehensive management using SCSI Enclosure Services.

An NVMe Enclosure may contain multiple Enclosure Services Processes. Communication and coordination between the Enclosure Services Processes that manage NVMe Enclosure elements is outside the scope of this specification.

# 1.3 Theory of Operation

This specification is designed to provide a common interface over multiple physical layers (i.e., PCI Express, SMBus/I2C) for inventory, monitoring, configuration, and change management. This specification provides the flexibility necessary to manage NVMe Storage Devices or NVMe Enclosures using an out-of-band mechanism or in-band tunneling mechanism in a variety of host environments and systems. This specification also defines a FRU Information Device that contains Vital Product Data (refer to section 1.3.1.2).

# 1.3.1 Out-of-Band Theory of Operation

This specification defines a mechanism for managing NVMe Storage Devices and NVMe Enclosures outof-band via the Management Component Transport Protocol (refer to section 1.3.1.1).

# 1.3.1.1 Management Component Transport Protocol

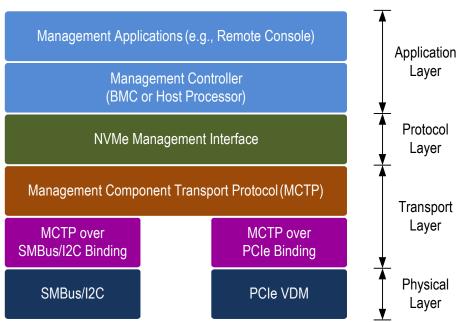

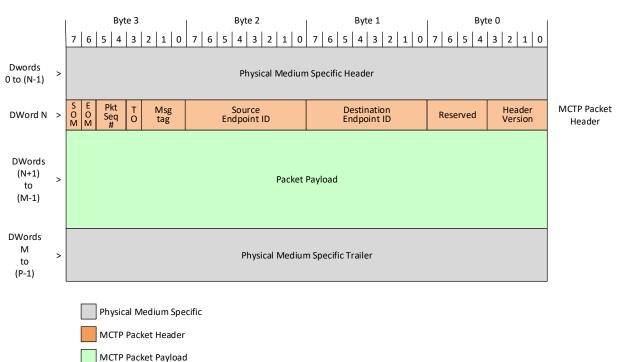

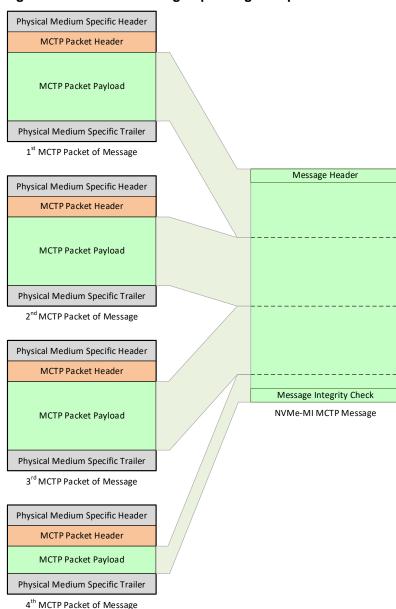

The out-of-band mechanism utilizes the Management Component Transport Protocol (MCTP) as the transport and utilizes existing MCTP SMBus/I2C and PCIe bindings for the physical layer. Command Messages are submitted to one of two Command Slots associated with a Management Endpoint contained in an NVM Subsystem. Figure 1 shows the NVMe-M out-of-band protocol layering.

# 1.3.1.2 FRU Information Device

This specification defines a mechanism to access a FRU Information Device either via SMBus/I2C as defined by the IPMI Platform Management FRU Information Storage Definition specification or via the VPD Read and VPD Write commands. The data stored in the FRU Information Device is referred to as Vital Product Data (refer to section 9.2). A FRU Information Device may be implemented in a variety of ways (e.g., a serial EEPROM, one-time programmable memory in an NVMe Controller ASIC, etc.).

# 1.3.2 In-Band Theory of Operation

This specification defines an in-band tunneling mechanism that utilizes the NVMe Admin Commands NVMe-MI Send and NVMe-MI Receive. Refer to the NVM Express specification and section 4.3 of this specification for additional details on the NVMe-MI Send and NVMe-MI Receive commands.

# 1.4 NVM Subsystem Architectural Model

This specification defines an interface that may be used to manage NVM Subsystems contained within an NVMe Storage Device or NVMe Enclosure.

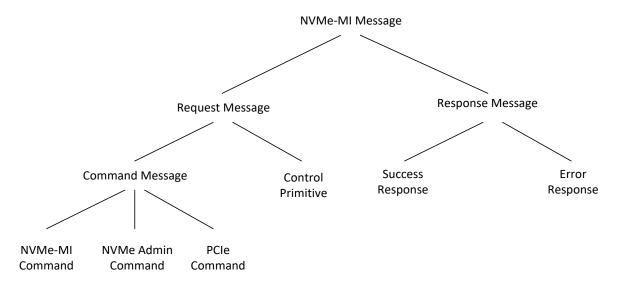

Management of an NVM Subsystem in the in-band tunneling mechanism and the out-of-band mechanism consists of sending Command Messages and receiving corresponding Response Messages. Command Messages consist of standard NVMe Admin Commands that target a Controller within the NVM Subsystem; commands that provide access to the PCI Express configuration, I/O, and memory spaces of a Controller in the NVM Subsystem; and Management Interface specific commands for inventorying, configuring, and monitoring of the NVM Subsystem. The Command Messages supported by an NVM Subsystem are dependent on the mechanism used to send the NVMe-MI Message (i.e., in-band tunneling mechanism or out-of-band mechanism) and whether the NVM Subsystem is contained within an NVMe Storage Device or NVMe Enclosure.

When using the in-band tunneling mechanism, the architecture and behavior of an NVM Subsystem is as defined by the NVM Express specification with extensions defined by this specification. The remainder of this section describes the architecture and behavior of an NVM Subsystem when the out-of-band mechanism is used.

The PCIe ports and SMBus/I2C port of an NVM Subsystem may optionally each contain a single NVMe Management Endpoint (hereafter referred to as simply Management Endpoint). A Management Endpoint is an MCTP endpoint that is the terminus and origin of MCTP packets/messages and is responsible for implementing the MCTP Base Protocol, processing MCTP Control Messages, and internal routing of Command Messages. Each Management Endpoint in an NVM Subsystem has a Port Identifier that is less than or equal to the Number of Ports (NUMP) field value in the NVM Subsystem Information Data Structure.

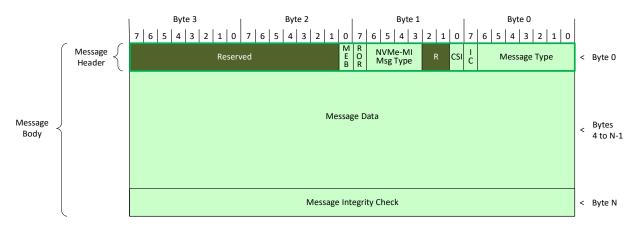

Management Interface Request Messages and Response Messages are transported as MCTP messages with the Message Type set to NVM Express Management Messages over MCTP (refer to the MCTP IDs and Codes specification). All out-of-band mechanism Command Messages originate with the Management Controller and result in a Response Message from a Management Endpoint.

Each Management Endpoint advertises its unique capabilities. All Management Endpoints may support the same commands even though PCIe ports are full duplex with much higher data rates than SMBus (i.e., both SMBus/I2C and PCIe VDM are capable of providing the same functionality).

Each NVMe Controller in the NVM Subsystem shall provide an NVMe Controller Management Interface (hereafter referred to as simply Controller Management Interface). The Controller Management Interface processes Controller operations on behalf of any Controller (in-band tunneling mechanism) or Management Endpoint (out-of-band mechanism) in the NVM Subsystem. Controllers or Management Endpoints may route commands to any NVMe Controller in the NVM Subsystem. A Controller Management Interface logically processes one operation at a time. A Controller Management Interface is not precluded from processing two or more operations in parallel; however, there shall always be an equivalent pattern of sequential operations with the same results.

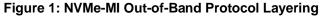

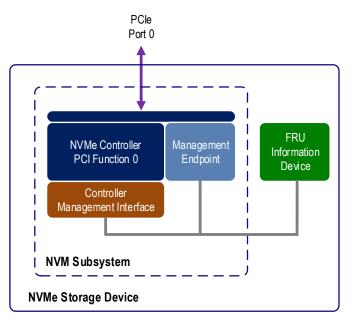

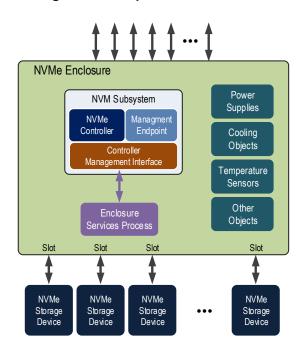

Figure 2 illustrates an example NVM Subsystem. The NVM Subsystem contains a single Controller and there is a Management Endpoint associated with the PCIe port.

# Figure 2: NVM Subsystem Associated with Single PCIe Port

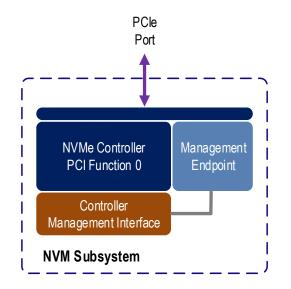

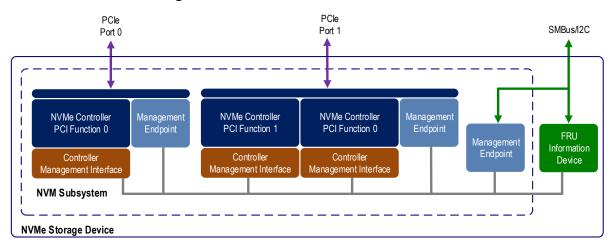

Figure 3 illustrates an example NVM Subsystem that is associated with a dual ported PCIe SSD. The NVM Subsystem contains one Controller associated with PCIe Port 0 and two Controllers associated with PCIe Port 1. There is a Management Endpoint associated with the each PCIe port and the SMBus/I2C port. Since the NVM Subsystem contains a Management Endpoint, all Controllers have an associated Controller Management Interface.

Figure 3: NVM Subsystem with Dual Ported PCIe Ports and an SMBus/I2C Port

# 1.5 NVMe Storage Device Architectural Model

The architectural model for NVMe Storage Devices that support the in-band tunneling mechanism follows the architectural model defined in the NVM Express specification.

An NVMe Storage Device that implements the out-of-band mechanism but not the in-band tunneling mechanism defined in this specification consists of zero or more NVM Subsystems. An NVMe Storage

Device that implements the in-band tunneling mechanisms defined in this specification consists of one or more NVM Subsystems. Each NVM Subsystem includes one or more Management Endpoints.

An NVMe Storage Device that is a Field-Replaceable Unit (FRU) is a physical component, device, or assembly that is able to be removed and replaced (e.g., by an end user or technician) without having to replace the entire system in which it is contained. Examples of NVMe Storage Device Field-Replaceable Units include a U.2 PCIe SSD, a PCI Express Card Electromechanical (CEM) add-in card, and an M.2 module. The FRU referenced by the FRU Globally Unique Identifier (FGUID) field in the NVM Express specification shall be an NVMe Storage Device Field-Replaceable Unit.

There are many variants of an NVMe Storage Device. One example is an NVMe Storage Device that only contains a single NVM Subsystem. Another example may contain no NVM Subsystems and instead have one or more Expansion Connectors for adding additional NVMe Storage Device FRUs. Such an NVMe Storage Device is referred to as a Carrier. In another example, the NVMe Storage Device may contain one or more NVM Subsystems and one or more Expansion Connectors. NVMe Storage Devices may contain PCIe switches which connect to one or more NVM Subsystems or Expansion Connectors. NVMe Storage Devices may contain SMBus/I2C Muxes that connect to one or more NVM Subsystems or Expansion Connectors.

This specification defines Vital Product Data (VPD) that utilizes the format defined in the IPMI Platform Management FRU Information Storage Definition and is stored in a FRU Information Device. VPD is accessible over any port that supports the out-of-band mechanism or in-band tunneling mechanism. If the NVMe Storage Device has an SMBus/I2C port, then the VPD is accessible using the access mechanism over I2C as defined in the IPMI Platform Management FRU Information Storage Definition.

If an NVMe Storage Device contains multiple NVM Subsystems, then the FRU Information Device associated with each NVM Subsystem is optional since the required FRU Information Device accessible via the Upstream Connector describes the entire NVMe Storage Device. The contents of these additional FRU Information Devices is out of scope for this specification. Refer to section 9.2 for more information

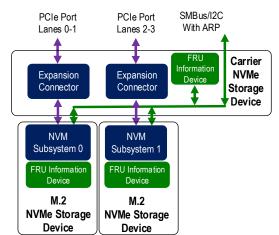

Figure 4 illustrates an NVMe Storage Device that is a single-port PCIe SSD with the FRU Information Device implemented by the NVM Subsystem. Figure 5 illustrates an NVMe Storage Device that is a dual-port PCIe SSD with an SMBus/I2C port and a FRU Information Device implemented using a Serial EEPROM.

# Figure 4: Single-Port PCIe SSD

Figure 5: Dual-Port PCIe SSD with SMBus/I2C

An example U.2 form factor NVMe Storage Device with Expansion Connectors (i.e., a Carrier) is shown in Figure 6. This Carrier has two M.2 Expansion Connectors for connecting two M.2 NVMe Storage Device FRUs. The Carrier and each M.2 NVMe Storage Device are separate NVMe Storage Device FRUs, each with their own FRU Information Device. The FRU Information Device on the Carrier is at address A4h and the FRU Information Devices on each M.2 NVMe Storage Device has a default address of A6h and supports the SMBus Address Resolution Protocol (ARP). ARP is used after power is applied to reassign the conflicting A6h addresses before the M.2 FRU Information devices are read. ARP would also be used to reassign the conflicting MCTP addresses and potentially additional elements.

Figure 6: NVMe Storage Device with Expansion Connectors (i.e., a Carrier)

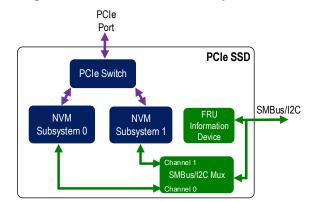

Figure 7 shows an NVMe Storage Device that contains two NVM Subsystems implemented using soldered down BGA packages and a FRU Information Device at address A6h. An NVMe Storage Device without Expansion Connectors that implements an SMBus/I2C port always contains a FRU Information Device at address A6h directly connected to the Upstream Connector. An SMBus/I2C Mux is used in this example instead of ARP to eliminate SMBus/I2C address collisions. The SMBus/I2C Mux is configured by a

Management Controller prior to communications with the selected NVM Subsystem. The FRU Information Device contains the details necessary to configure the SMBus/I2C Mux.

#### Figure 7: NVMe Storage Device with two NVM Subsystems and an SMBus/I2C Mux

#### 1.6 NVMe Enclosure Architectural Model

An NVMe Enclosure is a platform, card, module, box, rack, or set of boxes that may provide power, cooling, and mechanical protection for one or more NVM Subsystems. These NVM Subsystems may be part of the NVMe Enclosure itself and/or may be contained in NVMe Storage Devices FRUs that connect to the NVMe Enclosure through one or more NVMe Enclosure slots. An NVMe Enclosure contains one or more NVM Subsystems. NVM Subsystems that are part of an NVMe Enclosure may support just the in-band tunneling mechanism, just the out-of-band mechanism, or both.

An NVMe Enclosure may contain elements that support operation of the NVMe Enclosure (e.g., power supplies, fans, locks, temperature sensors, current sensors, and voltage sensors). An NVMe Enclosure may also contain displays and/or indicators that indicate the state of the NVMe Enclosure (e.g., state of elements, NVM Subsystems, or RAID volumes) and/or NVMe Storage Devices that connect to the NVMe Enclosure. Some of the elements that make up an NVMe Enclosure may be removable and replaceable while the NVMe Enclosure continues to operate normally.

SCSI Enclosure Services - 3 (SES-3) is a standard developed by the American National Standards Institute T10 committee for management of enclosures using the SCSI architecture. While the NVMe and SCSI architectures differ, the elements of an NVMe Enclosure and a SCSI enclosure are similar and the capabilities required to manage elements of an NVMe Enclosure and a SCSI enclosure are similar. Thus, this specification leverages SES for Enclosure Management. SES manages the elements of an enclosure using control and status diagnostic pages transferred using SCSI commands (refer to Enclosure Control and Enclosure Status diagnostic pages in SES-3). This specification uses these same control and status diagnostic pages but transfers them using the SES Send and SES Receive commands. this specification supports only the standalone Enclosure Services Process model as defined in SES.

A Requester manages an NVMe Enclosure using SES Send and SES Receive commands that are part of the Management Interface Command Set (refer to section 5). The SES Send command provides the functionality of the SES-3 SCSI SEND DIAGNOSTIC command and is used by a Requester to send SES control type diagnostic pages to modify the state of the NVMe Enclosure. The SES Receive command provides the functionality of the SES-3 SCSI RECEIVE DIAGNOSTIC RESULTS command and is used by a Requester to retrieve SES status type diagnostic pages that contain various status and warning information available from the NVMe Enclosure.

Refer to SES-3 for a list and description of SES control type diagnostic pages and SES status type diagnostic pages. The mapping of bytes in SES pages to NVMe-MI Request and Response Data is one-to-one where byte x of the SES page maps to byte x in the NVMe-MI Request or Response Data (e.g., byte zero of the SES control type diagnostic page corresponds to byte zero of NVMe-MI Request Data). The

NVMe firmware update process is used (i.e., Firmware Image Download and Firmware Commit commands) to update NVMe firmware. Download Microcode Control and Status diagnostic pages, if supported, shall only be supported on NVMe Enclosure elements.

An Enclosure Services Process, that is logically part of the NVMe Enclosure, is responsible for managing NVMe Enclosure elements and participates in servicing SES Send and SES Receive commands issued by a Requester. Unlike the SES-3 Enclosure Services Process model that maintains state for each I\_T nexus (refer to SES-3), unless otherwise noted, this specification requires an NVMe Enclosure to maintain a single global state regardless of the Requester or path used to access that state.

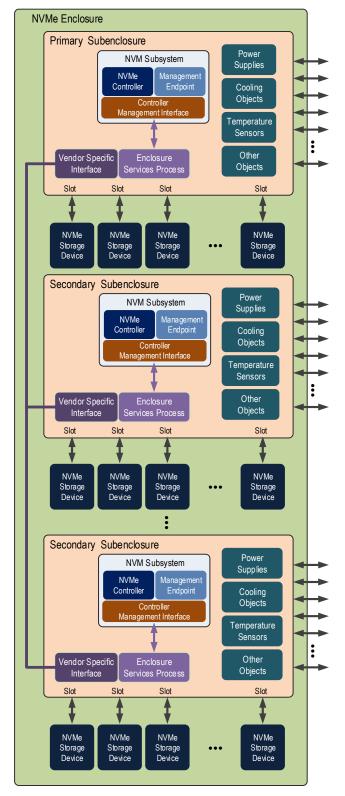

An NVMe Enclosure may contain of one or more Subenclosures (refer to SES-3). Each Subenclosure is identified by an SES-3 defined one-byte Subenclosure identifier. If multiple Subenclosures are present, then one of the Subenclosures is designated as the primary Subenclosure and the remaining Subenclosures are secondary Subenclosures. When an NVMe Enclosure consists of only a single Subenclosure, then that Subenclosure is the primary Subenclosure. The Enclosure Services Process associated with the primary Subenclosure is the one that provides access to NVMe Enclosure services information for all Subenclosures. Refer to SES-3 for more information.

Associated with each NVMe Enclosure slot is an SES element that may be used to manage the slot. Refer to SES-3 for more information.

Figure 8 illustrates an example NVMe Enclosure that contains one NVM Subsystem. This NVMe Enclosure has multiple ports that Requesters may use to communicate with the NVMe Enclosure. It also has multiple slots that are used to connect NVMe Storage Devices to the NVMe Enclosure (e.g., PCIe). The mapping of NVMe Enclosure ports to NVM Subsystems, NVMe Controllers within these NVM Subsystems, and NVMe Storage Devices is vendor specific and outside the scope of this specification. An NVMe Enclosure shall contain one or more NVM Subsystems used for Enclosure Management. The NVMe Enclosure in this example may be managed using the out-of-band mechanism via the Responder (Management Endpoint in Figure 8) or using the in-band tunneling mechanism via the NVMe Controller.

# Figure 8: Example NVMe Enclosure

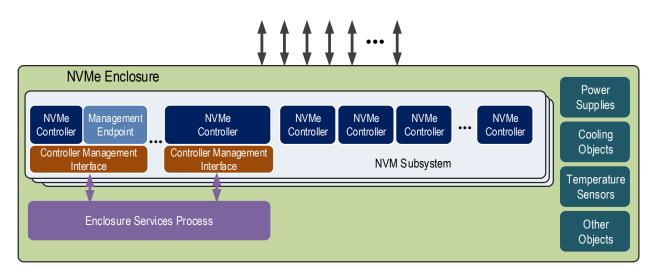

Figure 9 illustrates an example NVMe Enclosure that contains multiple NVM Subsystems and no NVMe Storage Devices. This may represent a software storage appliance. The NVM Subsystems and Controllers contained within these NVM Subsystems may be real or emulated in software. Not all Controllers within these NVM Subsystems are required to have the same capabilities. Some of the possible capability configurations are illustrated in this example. Some Controllers in this example simply provide access to namespaces; others provide access to namespaces and support for the in-band tunneling mechanism; and others provide access to namespaces and support for the out-of-band mechanism.

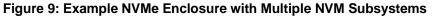

Figure 10 shows an Enclosure that supports two Enclosure Services Processes. Elements of the NVMe Enclosure may be accessible by one or both of these Enclosure Services Processes. The coordination of access to elements by multiple Enclosure Services Processes is outside the scope of this specification.

### Figure 10: Example NVMe Enclosure with Multiple Enclosure Services Processes

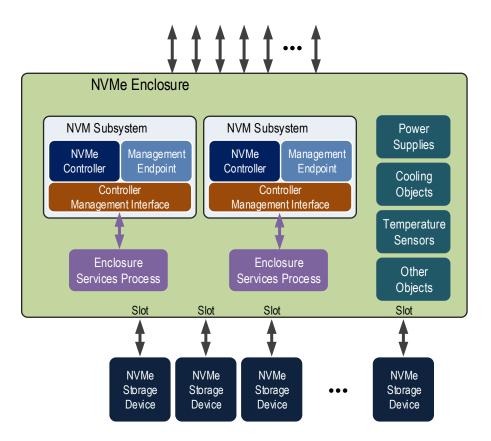

Figure 11 shows an NVMe Enclosure that consists of multiple Subenclosures. Each Subenclosure in this example contains an Enclosure Services Process. NVMe Enclosure services information from Subenclosures is combined into a single set of SES diagnostic pages by the primary Subenclosure. A Subenclosure identifier is used to distinguish from which Subenclosure the information was obtained. Refer to SES-3 for more information. A primary Subenclosure may access NVMe Enclosure services information in Subenclosures using the out-of-band mechanism, the in-band tunneling mechanism, or both; or may use a vendor specific interface. This example illustrates the use of a vendor specific interface.

Figure 11: Example NVMe Enclosure with Subenclosures

Certain NVMe Enclosure behaviors are managed by setting controls and testing status of elements within an NVMe Enclosure. An Enclosure Services Process may monitor a variety of warning and error conditions. These conditions may be communicated to the Requester through polling by the Requester (refer to Enclosure Services Management mode page in SES-3 for details).

The mapping of SES-3 sense keys and additional sense codes associated with CHECK CONDITION status to NVMe-MI Response Message Status values is shown in Figure 12. The asynchronous event notification reporting mechanism described in SES-3 is not supported by this specification.

| Response Message Status Values      | SES-3                     |                                |  |  |  |

|-------------------------------------|---------------------------|--------------------------------|--|--|--|

| Response message Status values      | Sense Key                 | Additional Sense Code          |  |  |  |

| Enclosure Services Failure          |                           | ENCLOSURE SERVICES FAILURE     |  |  |  |

| Enclosure Services Transfer Failure | HARDWARE ERROR            | ENCLOSURE SERVICES TRANSFER    |  |  |  |

| Enclosure Services Transfer Failure |                           | FAILURE                        |  |  |  |

| Enclosure Failure                   |                           | ENCLOSURE FAILURE              |  |  |  |

| Enclosure Services Transfer         | HARDWARE ERROR or ILLEGAL | ENCLOSURE SERVICES TRANSFER    |  |  |  |

| Refused                             | REQUEST                   | REFUSED                        |  |  |  |

| Unsupported Enclosure Function      | ILLEGAL REQUEST           | UNSUPPORTED ENCLOSURE FUNCTION |  |  |  |

| Enclosure Services Unavailable      | NOT READY                 | ENCLOSURE SERVICES UNAVAILABLE |  |  |  |

| Enclosure Degraded                  | RECOVERED ERROR           | WARNING – ENCLOSURE DEGRADED   |  |  |  |

Figure 12: Mapping of SES-3 Sense Keys and Additional Sense Codes to Response Message Status

# 1.7 Conventions

Hardware shall return zero for all bits, fields, and registers that are marked as reserved. The Requester should not rely on a value of zero being returned as future revisions of this specification may contain non-zero values. The Requester should write all reserved bits and registers with the value of zero. Future revisions of this specification may rely on a zero value being written for backward compatibility.

Hexadecimal (i.e., base 16) numbers are written with a lower case "h" suffix (e.g., 0FFFh, 80h). Hexadecimal numbers larger than eight digits are represented with an underscore character dividing each group of eight digits (e.g., 1E\_DEADBEEFh).

Binary (i.e., base 2) numbers are written with a lower case "b" suffix (e.g., 1001b, 10b). Binary numbers larger than four digits are written with an underscore character dividing each group of four digits (e.g., 1000\_0101\_0010b).

All other numbers are decimal (i.e., base 10). A decimal number is represented in this specification by any sequence of digits consisting of only the Western-Arabic numerals 0 to 9 not immediately followed by a lower-case b or a lower-case h (e.g., 175). This specification uses the following conventions for representing decimal numbers:

- a) the decimal separator (i.e., separating the integer and fractional portions of the number) is a period;

- b) the thousands separator (i.e., separating groups of three decimal digits in a portion of the number) is a comma;

- c) the thousands separator is used in only the integer portion of a number and not the fractional portion of a number; and

- d) the decimal representation for a year does not include a comma (e.g., 2018 instead of 2,018).

SMBus/I2C addresses are written as 8-bit hex values where bits 7:1 contain the 7-bit SMBus/I2C address and bit 0 is cleared to '0'.

When a register field is referred to in the document, the convention used is "Register Symbol.Field Symbol" (e.g., the Controller Status (CSTS) register Shutdown Status (SHST) field is referred to by the name

CSTS.SHST). If the register field is an array of bits, the field is referred to as "Register Symbol.Field Symbol (array offset to element)".

A 0's based value is a numbering scheme for which the number 0h represents a value of 1h and thus produces the pattern of 0h represents 1h, 1h represents 2h, 2h represents 3h, etc. In this numbering scheme, there is not a method for specifying the value of 0h. Values in this specification are 1-based (i.e., the number 1h represents a value of 1h, 2h represents 2h, etc.) unless otherwise specified.

Some parameters are defined as a string of ASCII or UTF-8 characters. ASCII data fields shall contain only code values 20h to 7Eh. UTF-8 is backwards compatible with ASCII encoding and supports additional characters with variable length encoding. For the string "Copyright", the character "C" is the first byte, the character "o" is the second byte, etc. The string is left justified and shall be padded with spaces (ASCII character 20h) to the right if necessary.

A range of numeric values is represented in this specification in the form "a to z", where a is the first value included in the range, all values between a and z are included in the range, and z is the last value included in the range (e.g., the representation "0h to 3h" includes the values 0h, 1h, 2h, and 3h).

Size values are shown in binary units or decimal units. The symbols used to represent these values are as shown in Figure 13.

| Decin                  | nal              | В         | inary           |

|------------------------|------------------|-----------|-----------------|

| Symbol Power (base-10) |                  | Symbol    | Power (base-2)  |

| kilo / k               | 10 <sup>3</sup>  | kibi / Ki | 2 <sup>10</sup> |

| mega / M               | 10 <sup>6</sup>  | mebi / Mi | 2 <sup>20</sup> |

| giga / G               | 10 <sup>9</sup>  | gibi / Gi | 2 <sup>30</sup> |

| tera / T               | 10 <sup>12</sup> | tebi / Ti | 2 <sup>40</sup> |

| peta / P               | 10 <sup>15</sup> | pebi / Pi | 2 <sup>50</sup> |

| exa / E                | 10 <sup>18</sup> | exbi / Ei | 2 <sup>60</sup> |

| zetta / Z              | 10 <sup>21</sup> | zebi / Zi | 2 <sup>70</sup> |

| yotta / Y              | 10 <sup>24</sup> | yobi / Yi | 2 <sup>80</sup> |

Figure 13: Decimal and Binary Units

Implementation Specific (Impl Spec) – the controller has the freedom to choose its implementation.

Hardware Initialize (HwInit) – The default state is dependent on NVM Express controller and system configuration. The value is initialized at reset (e.g., by an expansion ROM, or in the case of integrated devices, by a platform BIOS).

# 1.8 Definitions

# 1.8.1 Carrier

An NVMe Storage Device FRU with one or more Expansion Connectors and zero or more NVM Subsystems.

# 1.8.2 Command Message

A type of Request Message that contains an NVMe Admin Command, PCIe Command, or NVMe-MI Command.

# 1.8.3 Command Slot

A logical target within a Management Endpoint where a Management Controller sends a Request Message. Each Management Endpoint has exactly two Command Slots.

# 1.8.4 Control Primitive

Single-packet Request Messages sent from a Management Controller to a Management Endpoint to affect the servicing of a previously issued Command Message or get the state of a Command Slot and Management Endpoint. Control Primitives are applicable only in the out-of-band mechanism and are prohibited in the in-band tunneling mechanism.

# 1.8.5 NVMe Controller (Controller)

Refer to the NVM Express specification.

# **1.8.6** NVMe Controller Management Interface (Controller Management Interface)

An interface associated with each NVMe Controller in the NVM Subsystem that is responsible for processing management operations on behalf of a Management Endpoint.

# 1.8.7 Enclosure Management

The discovery, monitoring and control of elements that make up an NVMe Enclosure.

# 1.8.8 Enclosure Services Process

A process that implements Enclosure services for an NVMe Enclosure that supports Enclosure Management. Refer to SCSI Enclosure Services - 3 (SES-3) for more information.

# 1.8.9 Expansion Connector

A connector that allows an NVMe Storage Device FRU or cable to be attached or removed from a Carrier. Expansion Connectors may be empty or populated. A connector to a non-removable NVMe Storage Device is not an Expansion Connector.

# 1.8.10 Field-Replaceable Unit (FRU)

A physical component, device, or assembly in a system that is able to be removed and replaced (e.g., by an end user or technician) without having to replace the entire system in which it is contained. The Field-Replaceable Unit described in this specification is an NVMe Storage Device Field-Replaceable Unit (refer to section 1.8.19).

#### 1.8.11 FRU Information Device

A logical or physical device used to hold the VPD. A FRU Information Device may be implemented in a variety of ways (e.g., a serial EEPROM, one-time programmable memory in silicon, etc.).

# 1.8.12 In-Band

Per the Management Component Transport Protocol (MCTP) Overview White Paper, in-band management is management that operates with the support of hardware components that are critical to and used by the operating system. The in-band communication path defined by this specification is via the NVMe Admin Queue using the NVMe-MI Send and NVMe-MI Receive commands from host software to an NVMe Controller. Refer to the NVM Express specification and section 4.3 of this specification for additional details on the NVMe-MI Send and NVMe-MI Receive commands.

# 1.8.13 Management Controller

A device (e.g., Baseboard Management Controller) responsible for platform management that uses the NVM Express Management Interface to communicate to Management Endpoints.

# 1.8.14 Management Endpoint or NVMe Management Endpoint

An MCTP endpoint associated with an NVM Subsystem (e.g., an NVMe SSD or NVMe Enclosure) that is the terminus and origin of MCTP packets/messages and which processes Request Messages.

# 1.8.15 Management Endpoint Buffer

An intermediate buffer defined by this specification to allow servicing out-of-band NVMe-MI Messages that have a Message Body that is larger than the 4,224-byte limit that is specified by the NVMe Management Messages over MCTP Binding Specification.

# 1.8.16 NVMe Enclosure

A platform, card, module, box, rack, or set of boxes that may provide power, cooling, mechanical protection and/or external interfaces for zero or more NVMe Storage Device FRUs. An NVMe Enclosure contains one or more NVM Subsystems and one or more Enclosure Services Processes.

# 1.8.17 NVMe Processing

NVMe command processing as defined by the NVM Express specification. The term NVMe Processing is used to distinguish command processing as defined by the NVM Express specification from the Command Message processing defined by this specification (refer to section 1.8.24).

# 1.8.18 NVMe Storage Device

A logical or physical component, device, or assembly that contains at least one NVM Subsystem or Expansion Connector, at least one Upstream Connector, and at least one FRU Information Device. An NVMe Storage Device that implements the out-of-band mechanism contains at least one Management Endpoint and a Controller Management Interface per Controller. An NVMe Storage Device contains zero or more PCIe switches and SMBus/I2C Muxes. An NVMe Storage Device shall comply with the NVM Express specification. In this specification, NVMe Storage Devices shall also comply with this specification.

# 1.8.19 NVMe Storage Device FRU

An NVMe Storage Device that is able to be removed and replaced (e.g., by an end user or technician) without having to replace the entire system in which it is contained. Examples of NVMe Storage Device

Field-Replaceable Units include a U.2 PCIe SSD, a PCI Express Card Electromechanical add-in card, or an M.2 module.

#### 1.8.20 NVMe Subenclosure (Subenclosure)

A portion of an NVMe Enclosure accessed through a primary NVMe Enclosure's Enclosure Services Process. Refer to SCSI Enclosure Services - 3 (SES-3) for more information.

#### 1.8.21 NVMe-MI Message

A type of MCTP Message that is defined by this specification in sections 3.1 and 4.1. See the MCTP IDs and Codes specification and the NVMe Management Messages over MCTP Binding Specification for more details on this type of MCTP Message (note that NVMe-MI Messages are referred to as NVM Express Management Messages over MCTP in these specifications).

#### 1.8.22 NVM Subsystem

This specification extends the definition of an NVM Subsystem defined in the NVM Express specification (e.g., by adding a Management Endpoint, Controller Management Interface, etc.). NVMe Enclosures and NVMe Storages devices that are not Carriers have one or more NVM Subsystems. Carriers have zero or more NVM Subsystems.

#### 1.8.23 Out-of-Band

Per the Management Component Transport Protocol (MCTP) Overview White Paper, out-of-band management is management that operates with hardware resources and components that are independent of the operating system's control. The out-of-band communication paths supported by this specification are via MCTP over SMBus/I2C or MCTP over PCIe VDM from a Management Controller to a Management Endpoint. In addition, this specification supports the out-of-band access mechanism defined by the IPMI Platform Management FRU Information Storage Definition specification for accessing a FRU Information Device from a Management Controller over SMBus/I2C.

#### 1.8.24 Process

This is the state when a Command Message is processed. Processing of a Command Message consists of checking for errors with the Command Message and performing the actions specified by the Command Message. This state is applicable in both the out-of-band mechanism and the in-band tunneling mechanism. Refer to section 4.2 for additional details on the Process state in the out-of-band mechanism. Refer to section 4.3 for additional details on the Process state in the in-band tunneling mechanism.

This specification uses the terms process/processing/processed to refer to actions performed in the Process state. These terms are distinct from the NVMe Processing term used to describe NVMe command processing as defined by the NVM Express specification (refer to section 1.8.17 in this specification).

#### 1.8.25 Request Message

An NVMe-MI Message originating from a Requester. A Request Message may be a Command Message or a Control Primitive. Request Messages may be used in both the out-of-band mechanism and the in-band tunneling mechanism.

#### 1.8.26 Requester

The entity that sends Request Messages and receives Response Messages. For the out-of-band mechanism, the Requester is a Management Controller. For the in-band tunneling mechanism, the Requester is host software.

#### 1.8.27 Responder

The entity that receives Request Messages and sends back Response Messages. For the out-of-band mechanism, the Responder is a Management Endpoint. For the in-band tunneling mechanism, the Responder is an NVMe Controller.

#### 1.8.28 Response Message

An NVMe-MI Message originating from a Responder in response to a Request Message. Response Messages may be used in both the out-of-band mechanism and the in-band tunneling mechanism.

#### 1.8.29 SMBus/I2C Mux

A bidirectional SMBus/I2C fan-out multiplexer with one upstream channel and one or more downstream channels configured by an I2C command from a Management Controller to connect zero or more downstream channels to the upstream channel. Each downstream channel may be connected to devices with SMBus/I2C ports. This multiplexer permits multiple devices to use the same SMBus/I2C addresses as long as they are on separate channels.

#### 1.8.30 Upstream Connector

A connector on the NVMe Storage Device or NVMe Enclosure to which a Requester attaches. It may be a physical connector as in U.2 form factors, solder balls as in a BGA form factor, or PCB trace fingers as in a CEM Add in Card or EDSFF form factor. An Upstream Connector may include multiple communications ports, control signals, and power supply rails.

#### 1.8.31 VPD or Vital Product Data

Field-Replaceable Unit (FRU) Information which is stored in a FRU Information Device. This specification defines a standard VPD format for NVMe Storage Devices.

#### 1.9 Keywords

Several keywords are used to differentiate between different levels of requirements.

#### 1.9.1 mandatory

A keyword indicating items to be implemented as defined by this specification.

#### 1.9.2 may

A keyword that indicates flexibility of choice with no implied preference.

#### 1.9.3 optional

A keyword that describes features that are not required by this specification. However, if any optional feature defined by the specification is implemented, the feature shall be implemented in the way defined by the specification.

#### 1.9.4 R

"R" is used as an abbreviation for "reserved" when the figure or table does not provide sufficient space for the full word "reserved".

#### 1.9.5 reserved

A keyword indicating reserved bits, bytes, words, fields, and opcode values that are set-aside for future standardization. Their use and interpretation may be specified by future extensions to this or other specifications. A reserved bit, byte, word, field, or register shall be cleared to zero, or in accordance with a future extension to this specification. The recipient shall not check the value of reserved bits, bytes, words, or fields.

#### 1.9.6 shall

A keyword indicating a mandatory requirement. Designers are required to implement all such mandatory requirements to ensure interoperability with other products that conform to the specification.

# 1.9.7 should

A keyword indicating flexibility of choice with a strongly preferred alternative. Equivalent to the phrase "it is recommended".

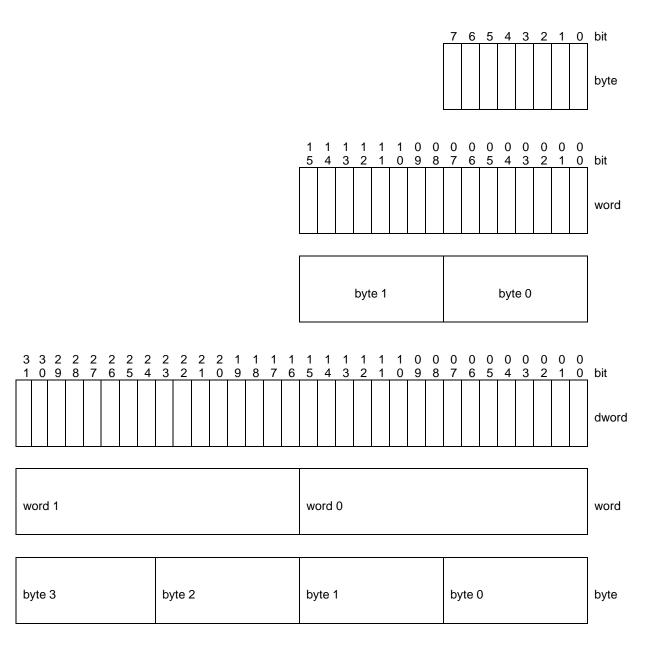

#### 1.10 Byte, Word, and Dword Relationships

Figure 14 illustrates the relationship between bytes, words, and dwords. This specification specifies data in a little-endian format.

Figure 14: Byte, Word, and Dword Relationships

#### 1.11 References

I2C Bus specification, revision 6.0. Available from http://www.i2c-bus.org

- IPMI Platform Management FRU Information Storage Definition 1.0, Version 1.3. Available from http://www.intel.com.

- INCITS 518-2017 Information Technology SCSI Enclosure Services 3 (SES-3). Available from https://webstore.ansi.org/.

MCTP Base Specification (DSP0236), version 1.3.0. Available from http://www.dmtf.org.

MCTP IDs and Codes (DSP0239), version 1.5.0. Available from http://dmtf.org.

MCTP Overview White Paper (DSP2016), version 1.0.0. Available from http://dmtf.org.

- MCTP PCIe VDM Transport Binding Specification (DSP0238), version 1.1.0. Available from http://www.dmtf.org.

- MCTP SMBus/I2C Transport Binding Specification (DSP0237), version 1.1.0. Available from http://www.dmtf.org.

NVM Express specification, revision 1.3a. Available from http://www.nvmexpress.org.

NVMe<sup>™</sup> (NVM Express<sup>™</sup>) Management Messages over MCTP Binding specification (DSP0235), revision 1.0.1. Available from http://www.dmtf.org.

PCI Express Base Specification, revision 4.0. Available from http://www.pcisig.com.

System Management Bus (SMBus) Specification, revision 3.1. Available from http://www.smbus.org.

# 2 Physical Layer

This section describes the physical layers supported by this specification for NVMe Storage Devices or NVMe Enclosures.

# 2.1 PCI Express

PCI Express is used as a physical layer in both the out-of-band mechanism and the in-band tunneling mechanism in this specification.

For the out-of-band mechanism, a PCIe port in an NVMe Storage Device or NVMe Enclosure may implement a Management Endpoint. If the PCIe port implements a Management Endpoint, the PCIe port shall support MCTP over PCIe Vendor Defined Messages (VDMs) as specified by the Management Component Transport Protocol (MCTP) PCIe VDM Transport Binding Specification.

For the in-band tunneling mechanism, host software issues NVMe Admin Commands (NVMe-MI Send and NVMe-MI Receive) to the NVMe Admin Queue over PCI Express. Refer to the NVM Express specification and section 4.3 of this specification for additional details on the NVMe-MI Send and NVMe-MI Receive commands.

# 2.2 SMBus/I2C

This section defines the requirements for an NVMe Storage Device or NVMe Enclosure that implements an SMBus/I2C port. The SMBus/I2C physical layer is only applicable for the out-of-band mechanism.

If an NVMe Storage Device or NVMe Enclosure implements an NVM Subsystem with a Management Endpoint associated with an SMBus/I2C port, then that port shall comply to the Management Component Transport Protocol (MCTP) SMBus/I2C Transport Binding Specification.

An NVM Subsystem may also support the NVMe Basic Management Command for health and status polling. The NVMe Basic Management Command is defined as an informative technical note in Appendix A, though it is not recommended for new designs.

Figure 15 lists SMBus/I2C elements that are supported on an NVMe Storage Device or NVMe Enclosure. For each SMBus/I2C element, the default SMBus/I2C address is provided as well as the conditions under which the SMBus/I2C element is required on an NVMe Storage Device or NVMe Enclosure. The presence or absence of Expansion Connectors on an NVMe Storage Device determines which of the two mutually exclusive SMBus/I2C addresses is used for the FRU Information Device. Using a different SMBus/I2C address for the FRU Information Device on NVMe Storage Devices that are Carriers versus non-Carriers avoids SMBus/I2C address conflict when Expansion Connectors are populated with NVMe Storage Devices.

ARP support on SMBus/I2C elements is optional unless there are multiple SMBus/I2C elements in the NVMe Storage Device or NVMe Enclosure with the same default SMBus/I2C address are present on the same SMBus/I2C channel.

| SMBus/I2C<br>Element         | Required Element Pre |                            | Required Element Presence |                                                                                                                                       |  |

|------------------------------|----------------------|----------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|

| Liement                      | Hex<br>Format        | Binary Format <sup>1</sup> | oupport                   |                                                                                                                                       |  |

| FRU<br>Information<br>Device | A6h                  | 1010_011xb                 | Optional                  | Required on an NVMe Storage Device with <i>no</i> Expansion Connectors. Undefined on NVMe Enclosures.                                 |  |

| FRU<br>Information<br>Device | A4h                  | 1010_010xb                 | Optional                  | Required on Carriers (i.e., an NVMe Storage<br>Device with <i>one or more</i> Expansion Connectors).<br>Undefined on NVMe Enclosures. |  |

Figure 15: SMBus/I2C Elements and Requirements

| SMBus/I2C<br>Element                        | Default SMBus/I2C Address |                            | SMBus ARP<br>Support | Required Element Presence                                                                                                                                                                                    |  |

|---------------------------------------------|---------------------------|----------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Liement                                     | Hex<br>Format             | Binary Format <sup>1</sup> | Support              |                                                                                                                                                                                                              |  |

| SMBus/I2C<br>Management<br>Endpoint         | 3Ah                       | 0011_101xb                 | Optional             | Required if an NVMe Storage Device or NVMe<br>Enclosure an SMBus/I2C Management Endpoint.                                                                                                                    |  |

| SMBus/I2C<br>Mux                            | E8h                       | 1110_100xb                 | Optional             | For NVMe Storage Devices, required if there is<br>more than one SMBus/I2C element on any<br>SMBus/I2C channel with the same SMBus/I2C<br>address that does not support ARP. Undefined on<br>NVMe Enclosures. |  |

| Basic<br>Management<br>Command <sup>2</sup> | D4h                       | 1101_010xb                 | Optional             | For NVMe Storage Devices, not recommended for new designs. Undefined on NVMe Enclosures.                                                                                                                     |  |

| NOTES:                                      |                           |                            |                      |                                                                                                                                                                                                              |  |

| Figure 15: SMBus/I2C Elements and Requirements   |   |

|--------------------------------------------------|---|

| rigule 13. Silibus/120 Elements and Requirements | , |

1. The x represents the SMBus/I2C read/write bit.

2. The NVMe Basic Management Command is defined in Appendix A as an informative technical note.

Host platforms expecting to be used with one or more Management Endpoints (e.g., data center platforms and workstations) should isolate SMBus/I2C channels to avoid a Management Endpoint conflicting with the address of another SMBus/I2C element. An SMBus/I2C address conflict may occur when a Management Endpoint that does not support ARP is used with platforms that do not isolate SMBus/I2C channels (e.g., some client platforms). ARP may be used to dynamically reassign SMBus/I2C addresses in a system when supported by both the Management Controller and the NVMe Storage Devices or NVMe Enclosure.

SMBus/I2C elements that support ARP should be implemented as Default Slave Address (DSA) devices as defined by the SMBus specification. These devices should not issue "Notify ARP Master" commands.

If ARP is supported by an NVM Subsystem, then all SMBus/I2C elements associated with that NVM Subsystem shall use the SMBus Address Resolution Protocol Unique Device Identifier (UDID) shown in Figure 16. The ARP UDID is a unique identifier. The UDID Vendor ID bits 30 and 31 allow up to four SMBus/I2C elements to be grouped together with the same NVM Subsystem. The only difference within this group of UDIDs is the most significant two bits of the Vendor Specific ID. This fact may be used by the Management Controller to associate an SMBus/I2C Management Endpoint with its corresponding FRU Information Device.

If there are multiple NVM Subsystems in an SMBus ARP-capable NVMe Storage Device or NVMe Enclosure, then the Unique NVM Storage Device ID field of the UDID shall be incremented by one for each NVM Subsystem. If the Upstream Connector has an SMBus/I2C port, then the FRU Information Device associated with that connector shall be present directly on the SMBus/I2C channel connected to the Upstream Connector.

Clock stretching is allowed by the Management Controller, Management Endpoint, and the FRU Information Device. However, implementations are strongly discouraged from using clock stretching so that communications are more predictable with higher throughput.

When a NACK is received, a Management Endpoint shall follow the MCTP SMBus/I2C Transport Binding Specification for a non-bridge endpoint. The Management Endpoint treats a STOP condition due to excessive SMBus NACKs as an implicit Pause Control Primitive. Refer to section 4.2.1.1.

| Bits    | Field                   | Description |                                                                                                                                                      |  |  |

|---------|-------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|         |                         | This field  | describes the device capabilities.                                                                                                                   |  |  |

|         |                         |             |                                                                                                                                                      |  |  |

|         | <b>D</b>                | Bits        | Description                                                                                                                                          |  |  |

| 127:120 | Device<br>Capabilities  | 7:6         | Address Type: This field describes the type of address contained in the                                                                              |  |  |

|         | Capabilities            | 5.1         | device. Refer to the MCTP SMBus/I2C Transport Binding Specification.<br>Reserved                                                                     |  |  |

|         |                         | 5:1         | <b>PEC Supported:</b> All MCTP transactions shall include a Packet Error Code                                                                        |  |  |

|         |                         | 0           | (PEC) byte. This bit shall be set to '1' to indicate support for PEC.                                                                                |  |  |

|         |                         | This field  | is used to identify the UDID version and silicon revision.                                                                                           |  |  |

|         |                         |             |                                                                                                                                                      |  |  |

|         | Varaian and             | Bits        | Description                                                                                                                                          |  |  |

| 119:112 | Version and<br>Revision | 7:6         | Reserved                                                                                                                                             |  |  |

|         | Revision                | 5:3         | <b>UDID Version:</b> This field specifies the UDID version and shall be set to 001b.                                                                 |  |  |

|         |                         | 2:0         | <b>Silicon Revision ID:</b> This field is used to specify a vendor specific silicon revision level.                                                  |  |  |

| 111:96  | Vendor ID               | This field  | contains the PCI-SIG vendor ID for the Management Endpoint.                                                                                          |  |  |

| 95:80   | Device ID               |             | contains a vendor assigned device ID for the Management Endpoint.                                                                                    |  |  |

| 00.00   | Dotted ID               |             | defines the SMBus version and the Interface Protocols supported.                                                                                     |  |  |

|         |                         |             |                                                                                                                                                      |  |  |

|         |                         | Bits        | Description                                                                                                                                          |  |  |

|         |                         | 15:08       | Reserved                                                                                                                                             |  |  |

|         |                         | 07          | <b>ZONE:</b> This bit shall be cleared to '0'.                                                                                                       |  |  |

| 79:64   | Interface               | 06          | <b>IPMI:</b> This bit shall be cleared to '0'.                                                                                                       |  |  |

|         |                         |             | ASF: This bit shall be set to '1'. Refer to the MCTP SMBus/I2C Transport                                                                             |  |  |

|         |                         | 05          | Binding Specification.                                                                                                                               |  |  |

|         |                         | 04          | OEM: This bit shall be set to '1'.                                                                                                                   |  |  |

|         |                         | 03:00       | <b>SMBus Version:</b> This field shall be set to 4h for SMBus Version 2.0, or to 5h for SMBus Version 3.0 and 3.1.                                   |  |  |

| 63:48   | Subsystem<br>Vendor ID  | This field  | his field contains the PCI-SIG vendor ID for the Management Endpoint.                                                                                |  |  |

| 47:32   | Subsystem<br>Device ID  | This field  | This field contains a vendor assigned device ID for the Management Endpoint.                                                                         |  |  |

|         | 20110010                | This field  | ensures all UDIDs from a vendor are unique and is used to associate elements                                                                         |  |  |

|         |                         |             | ted within an NVMe Storage Device or NVMe Enclosure.                                                                                                 |  |  |

|         |                         |             | -                                                                                                                                                    |  |  |

|         |                         | Bits        | Description                                                                                                                                          |  |  |

|         |                         | -           | UDID Type: This field distinguishes which NVM Subsystem that implements                                                                              |  |  |

|         |                         |             | multiple SMBus elements is providing the UDID. Note that Management                                                                                  |  |  |

|         |                         |             | Controllers implemented prior to NVMe-MI 1.1 may be incompatible with                                                                                |  |  |

|         | Vendor                  |             | devices using values 1h and 3h.                                                                                                                      |  |  |

| 31:00   | Specific ID             | 31:30       |                                                                                                                                                      |  |  |

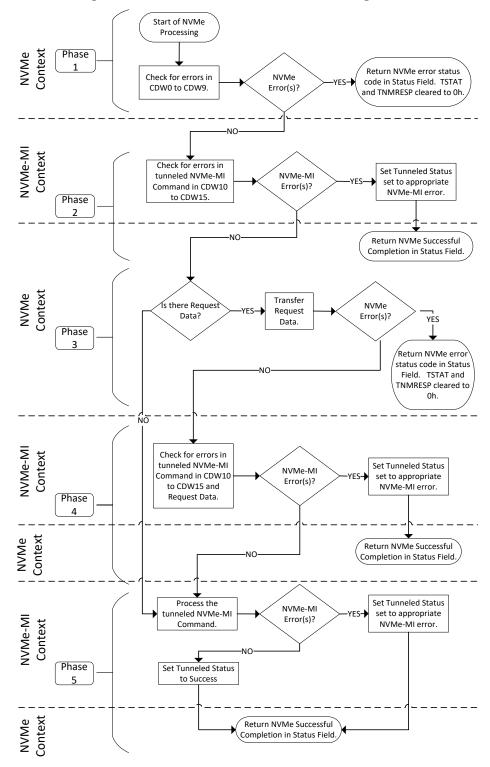

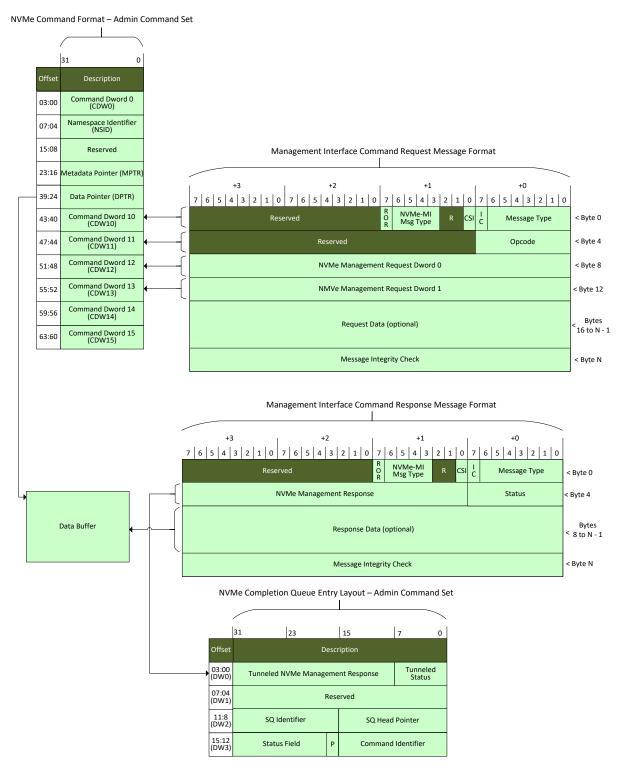

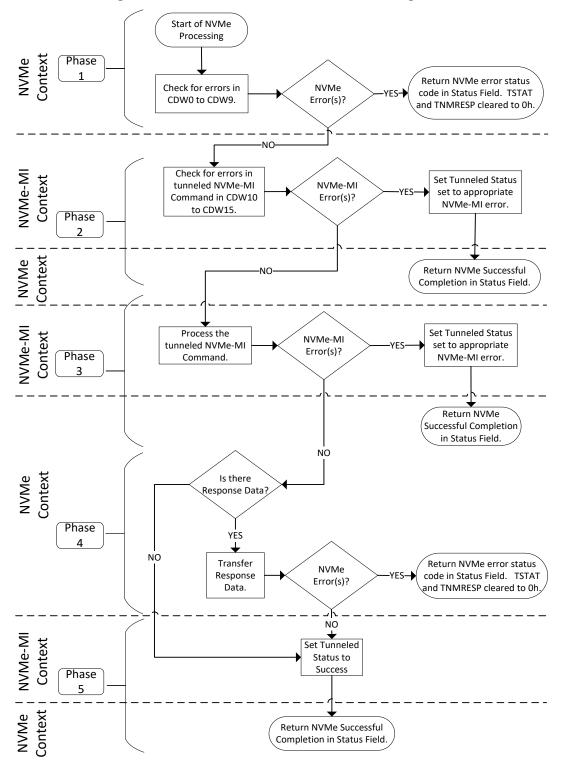

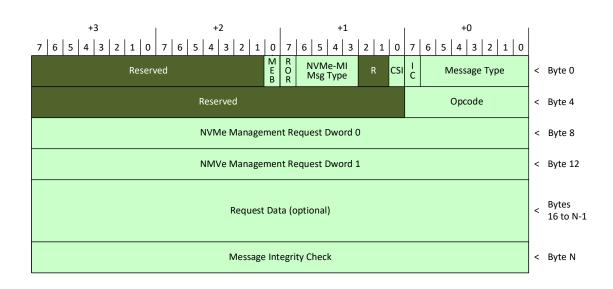

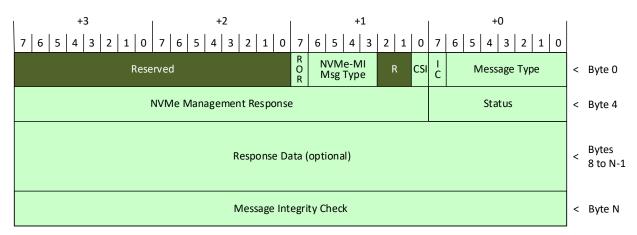

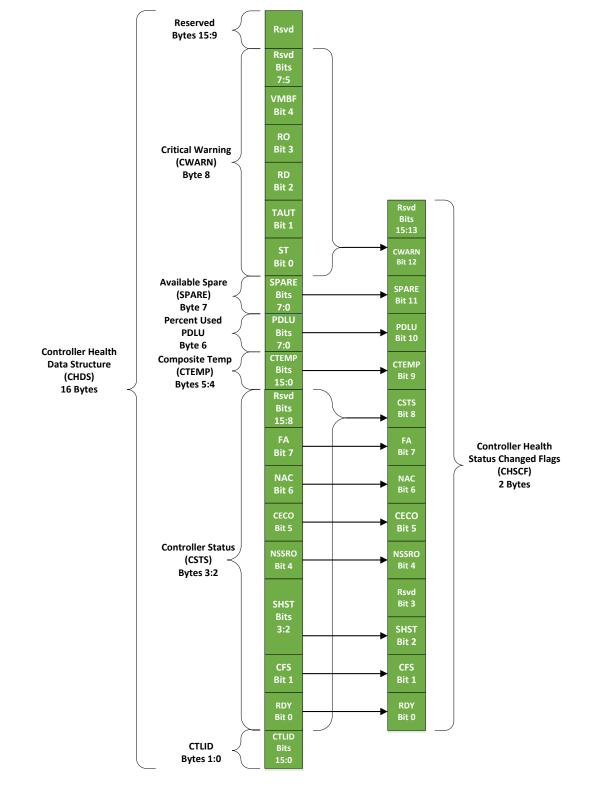

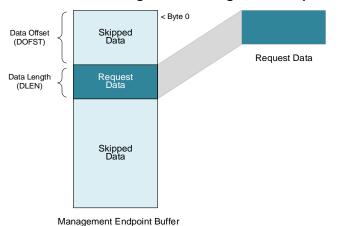

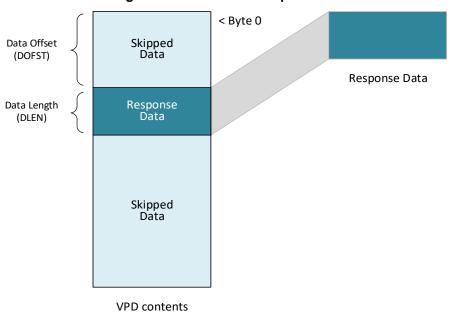

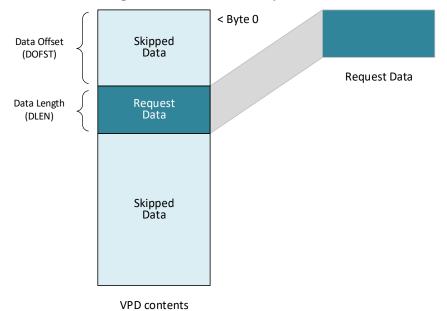

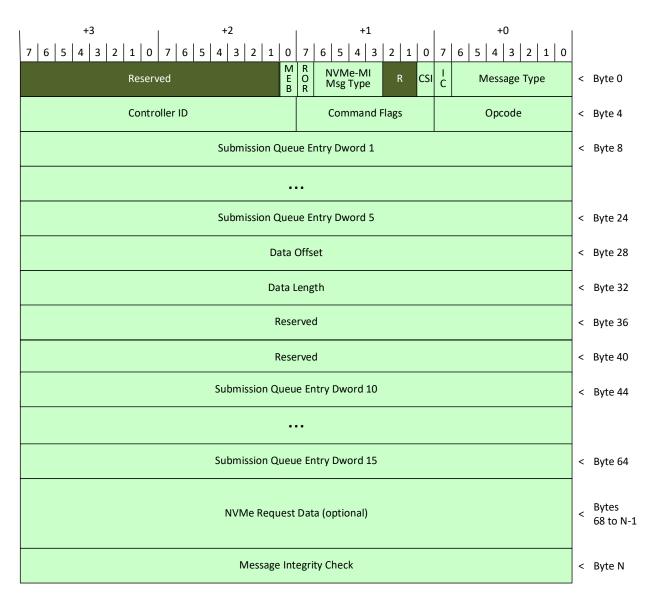

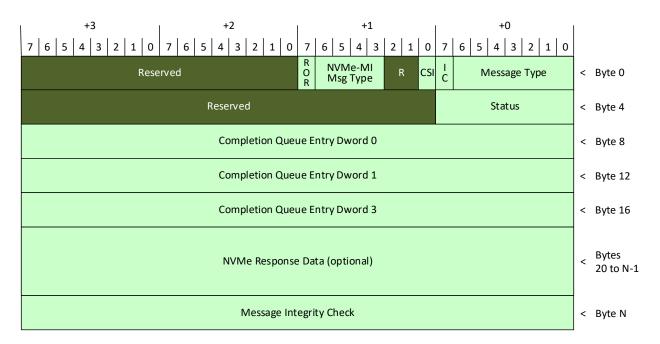

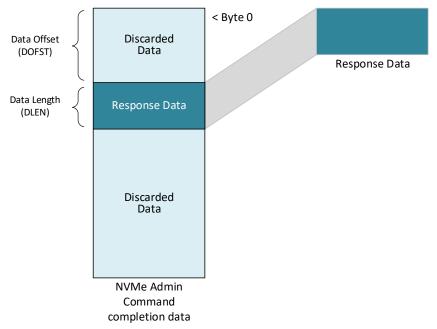

|         |                         | 01.00       | Value Description                                                                                                                                    |  |  |